分段路由 (SR) 可改变网络基础设施处理数据包的方式,从而实现更出色的网络性能。它用于互联网的核心以及数据中心内或数据中心之间。SR 可以用于分别在电信系统和网络系统中使用的多协议标签交换 (MPLS) 和 IPv6 数据平面。

SR 是一种简单的网络控制方法,使用源路由对数据包路由进行预编程,对数据包处理进行预调度并实施流量工程策略。

网络功能虚拟化 (NFV) 和软件定义网络 (SDN) 设备与系统供应商日益认识到,标准网络接口卡 (NIC) 产品在支持新兴的 NFV/SDN 工作负载方面可能存在性能限制。克服针对 SR 应用的这些性能限制可能需要加载更多的服务器计算资源,从而减少用于实施实际虚拟网络功能 (VNF) 的资源量。即使这种额外的网络开销可以接受,与在硬件中实现这些网络功能相比,额外的工作负载也可能导致整体系统性能的可预测性降低。

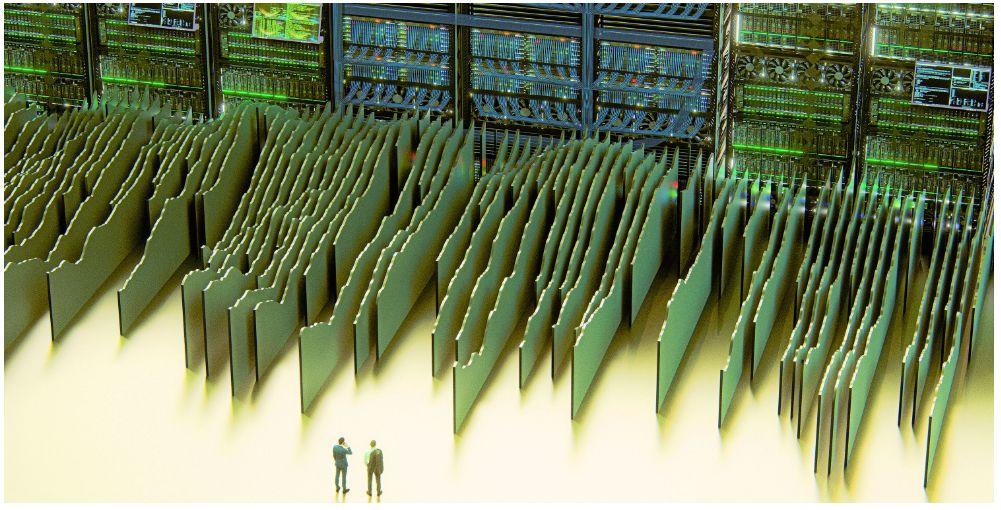

英特尔® FPGA 加速解决方案允许将特定的底层网络功能(例如 SR)卸载到硬件,通过节省 CPU 内核和周期来提高数据路径性能并提高可预测性。这些回收的 CPU 服务器资源可用于执行 VNF 和其他工作负载。

英特尔® FPGA 可编程加速卡 (PAC) N3000 是一种基于 FPGA 的解决方案,可通过编程处理几乎任何类型的功能(包括网络功能),从而提高网络和服务器性能。

HCL Technologies 和英特尔准备了《使用英特尔® FPGA 可编程加速卡 N3000 实施 IPv6 分段路由加速》白皮书。该白皮书描述了使用 FPGA 技术提高硬件性能的基于硬件的 SR 解决方案。