在进行FPGA设计时,大多数开发人员使用 JTAG 调试设计。然而,串行 JTAG 接口并非用于监控实时系统的高速接口。即使在设计中嵌入逻辑分析以捕捉轨迹时,JTAG 接口也可能成为性能瓶颈。

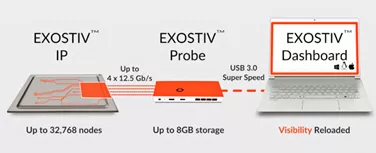

EXOSTIV 实验室研发了一种高速方法,可以深入了解基于 FPGA 的设计,以便您在设计投产之前就可以发现设计漏洞。该方法结合了多达16个在FPGA上实例化的逻辑分析器IP内核“捕获单元”,以监视设计中多达32,768个内部节点。该 IP 集成了类似逻辑分析器的触发器,但通过高速连接至外部探头模块,存储多达 8GB 已采集的数据。通过监控如此多的内部节点,并通过高速连接 EXOSTIV 探头,灵活传输已存储的数据,该方法显著提高了调试的可见性。

· 水平或过渡

· AND(和)、OR(或)、范围条件

· 数据验证(数据过滤)

· 路线图中的顺序触发

· 同时触发 1-16 个捕捉单元

· 交叉时钟域触发

FPGA 与 EXOSTIV 探头模块之间的高速连接能够以 50 Gbps 的速率将数据从 FPGA 发送至探头模块,如图 1 所示。

图 1:FPGA 中的 EXOSTIV IP 与外部探头模块以高达 50 Gbps 的速度通信,采集实时调试数据。

目前,EXOSTIV IP 和探头兼容英特尔® Stratix® 10、英特尔® Arria® 10 和英特尔® Cyclone® 10 FPGA,EXOSTIV 软件兼容英特尔® Quartus® Prime 软件套件。EXOSTIV 提供一个 EP6000 探头和一个 EP12000 探头,前者以每通道高达 6.6 Gbps 的速度运行,后者以每通道高达 12.5 Gbps 的速度运行。两个探头均提供单通道、双通道和四通道版本。