SPI(Serial Peripheral Interface)串行外设接口是Motorola公司在2000年推出的一种同步接口。这种接口首先由Motorola 公司在80年代中期开发,后来逐步成为行业标准。那么什么是SPI呢?它是一种高速、全双工的同步串行控制总线,主要用于芯片间的传输。相比较其他常用的通讯协议或接口,比如I2C,UART或其他并行总线等,SPI的优缺点列举如下:

优点:

硬件实现简单,

通讯线比较少(通常4 pin,有利于芯片封装),

通讯速度比较快(相对于I2C,UART,有些芯片可以达到133Mbit/s),

PCB 布线比较容易,

驱动程序相对简单。

缺点:

数据没有应答, 需要上层硬件,软件来保证传输数据的正确性。

不适合长距离传输,主要用于板内或板间数据传输。

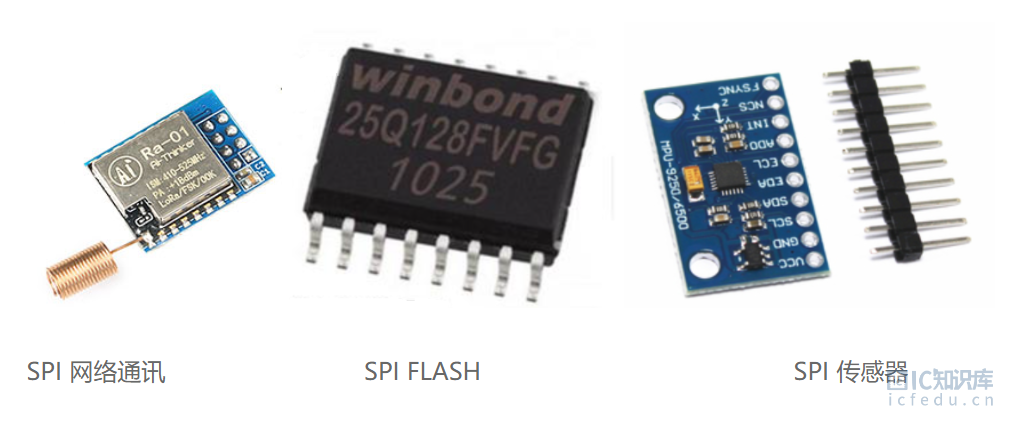

SPI接口被广泛的应用在串行FLASH存储器、EEPROM、AD转换芯片、液晶显示屏,解码器和各类传感器芯片中。

图1 SPI的应用场景

SPI 一主一从 连接

图2 一主一从SPI接口

其中, 主芯片 发送 SCLK,MOSI, #SS ; 主芯片接收 MISO信号。

SPI接口信号:

SCLK – Serial Clock (时钟信号,由主设备产生输出);

MOSI– Master Output Slave Input (主设备数据输出,从设备数据输入);

MISO– Master Input Slave Output (主设备数据输入,从设备数据输出);

#SS– Chip Select (从设备使能信号,由主设备控制, 输出)。

SPI 是一种同步全双工的接口, 主设备发出时钟(SCLK),片选信号(#SS),MOSI 数据信号;

从设备使用主设备的时钟,返回(输出)MISO 信号 给主设备

SPI 一主多从 连接

图3 一主多从SPI接口

主设备可以有多个片选(#SS )信号,每个#SS信号分别对应一个从设备, 一般情况下,#SS信号为低电平有效,但不是绝对的, 需要查看相关的设备手册(也有高电平有效的设备)

所有MISO 信号(从设备发出)共用一条MISO 信号线。

没有被#SS选择的设备,设备内部的MISO 需要高阻,这样就不影响其他从设备返回数给主设备。

从设备共用主设备发出的SCLK, MOSI信号 (广播)。

SPI的数据传输

SCLK 由主设备发出,通常情况下, 时钟速率没有强制规定, 主要看从设备的接受能力,不能超过从设备所规定的时钟速率即可。

MOSI和MISO线在SCLK的每个时钟周期传输一位数据,一般情况下(绝大多数)先发送最数据最高位MSB;最后发送数据最低位LSB。

SPI的四种通讯模式

四种模式的主要用来区分总线空闲时SCLK的状态 CPOL(clock polarity)和数据采样位置CPHA(clock phase)。其中CPOL和CPHA又被称为时钟极性CPOL(0,1)和 时钟相位CPHA(0,1)。 这两个概念,主要是用于兼容不同的从设备的需求而产生的通讯模式。 因此,由CPOL和CPHA的组合而产生了四种通讯模式,如图4所示。

CPOL(0,1):没有数据传输时,空闲状态时,时钟的电平。其中括号中的0和1分别表示低电平和高电平。

CPHA(0,1):数据在什么位置采样。括号中的0表示片选有效后第一个边沿采样, 1 表示片选有效后第二个边沿采样。

图4 时钟极性和相位时序图

图4中,时钟极性和相位可以分为以下四种组合:

CPHA = 1 ; 表示在片选后(片选信号有效),第二个时钟边沿 采集数据。同时还要看CPOL的初始状态(片选有效时)。

CPOL = 0 , 表示 初始SCLK电平为低,所以在SCLK的下降沿作为数据采样

CPOL = 1 , 表示 初始SCLK电平为高,所以在SCLK的上升沿作为数据采样

CPHA = 0 ; 表示在片选后(片选信号有效),第一个时钟边沿 采集数据。同时还要看CPOL的初始状态(片选有效时)。

CPOL = 0 , 表示 初始SCLK电平为低,所以在SCLK 的上升沿作为数据采样

CPOL = 1 , 表示 初始SCLK电平为高,所以在SCLK的下降沿作为数据采样

四种工作模式如表1所示。表1中所列出的四种模式通常被称作 mode 0,mode 1,mode 2和mode 3。

表1:

SPI 数据通讯方式

所有数据都是根据SCLK时钟信号进行 数据转换, 或者 数据采样的。 即SPI 是同步传输协议。具体情况(时钟上升沿是数据采样或者数据转换, 时钟下降沿是数据采样或者数据转换)根据SPI 的4种通讯模式。

如果需要片选信号,一定是在片选信号有效的情况下,遵循SPI 的4种通讯方式; 在片选无效时, 根据CPOL 的定义, 保持SCLK在高电平(CPOL = 1),或者低电平(CPOL = 0)。在有些一主一从的情况下, 可能不需要片选,这时默认片选是一直有效的。

数据传输没有规定需要多少个时钟周期,算是一个完整的操作。通常是 8, 16,24, 32个SCLK时钟周期等等。 根据从设备的定义,能够完成从设备的操作即可。

举例:

图5

图5所示:主设备发送8-bit命令

图6

图6所示:主设备发送8-bit 命令, 从设备返回24-bit 的数据给主设备。

图7

图7所示:主设备发送8-bit 命令, 发送 24-bit 的地址; 从设备返回24-bit地址所存储的数据。

对于数据传输来说,通讯的内容,由主从设备共同决定(从设备指出什么样的通讯可以被接受,主设备根据从设备的需求,编写相关的驱动)。

数据通讯没有应答信号(这个与IIC是不同的),所以通讯时,无法保证对方一定正确接收到发送的数据。 需要上层(软件, 硬件)校验,来保证数据传输的正确性。

SPI总线是全双工同步通讯总线, 即发送时也可以接收数据。但在一般情况下的应用是问答方式进行的。 即发送时,不接收数据; 接收时,不发送数据。 但没有明确规定,必须以这种半双工模式通讯。

声明:文章来源于IC知识库,本文内容及配图的版权归版权所有人所有,内容仅代表作者个人观点,不代表本网站观点或证实其内容的真实性。对于本网刊载的各类评论非本网评论员评论,仅代表评论者个人观点,并不代表本网证实或赞成其描述。如其他媒体、网站或个人转载使用,需保留本网注明的“稿件来源”,并自负法律责任。本文转载仅为更好的传播行业信息,若有内容图片侵权或者其他问题,请及时通过邮件联系我们,以便做侵删处理。